# Sequential Logic

CSCI 2050U - Computer Architecture

Randy J. Fortier

@randy\_fortier

# Outline

- Flip flops

- Registers

- Counters

- RAM

- The memory hierarchy

# Flip Flops

CSCI 2050U - Computer Architecture

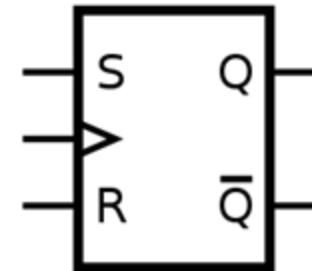

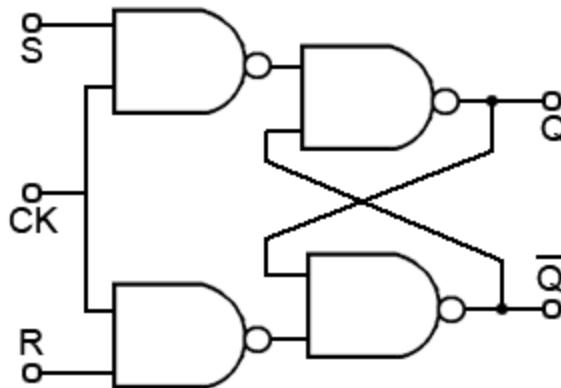

# SR Flip Flops

- The main issue with latches is that changes to the inputs start changing the value instantly

- To control when values update, we use an SR *flip flop*

- Flip flops are (clock) *edge triggered*

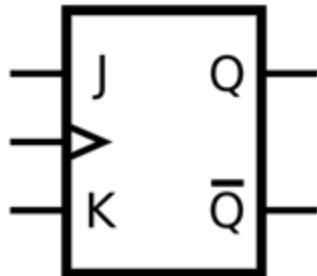

# JK Flip Flops

- A JK flip flop is identical to an SR flip flop, except:

- It uses the S=1, R=1 input combination

- S and R are called J and K, since they don't strictly mean set and reset, anymore

- When J = 1 and K = 1, the bit is flipped/complemented ( $0 \rightarrow 1, 1 \rightarrow 0$ )

| <b><i>J</i></b> | <b><i>K</i></b> | <b><i>Q<sub>i+1</sub></i></b> |

|-----------------|-----------------|-------------------------------|

| 0               | 0               | $Q_i$                         |

| 0               | 1               | 1                             |

| 1               | 0               | 0                             |

| 1               | 1               | $Q_i'$                        |

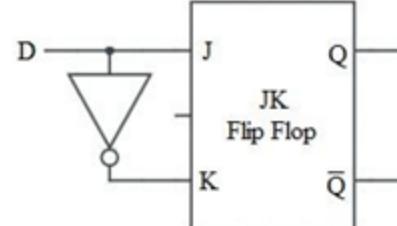

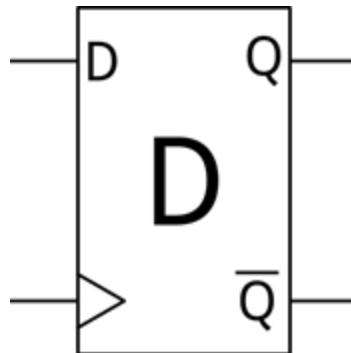

# D Flip Flops

- A D flip flop a much simpler concept:

- It has one input, D

- When D = 1, the value is set to 1

- When D = 0, the value is set to 0

| <b>D</b> | <b><math>Q_{i+1}</math></b> |

|----------|-----------------------------|

| 0        | 0                           |

| 1        | 1                           |

# Registers

CSCI 2050U - Computer Architecture

# Registers

- A register is a high-speed memory component accessible to the CPU

- Special-purpose registers:

- Program counter: Address of the next instruction to be executed

- Memory address register: Address for memory storage/retrieval

- Memory buffer register: Value to be stored to/the value retrieved from memory

- Status register: A set of flags used for signalling (e.g. carry, overflow)

- General-purpose registers:

- Registers used as operands in arithmetic operations

# Registers

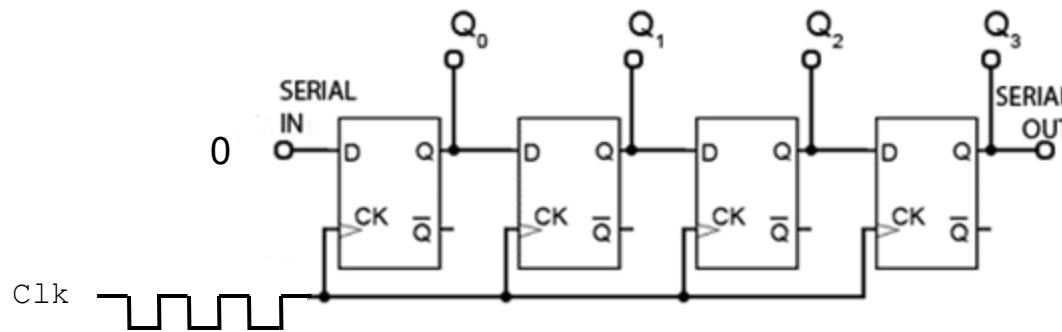

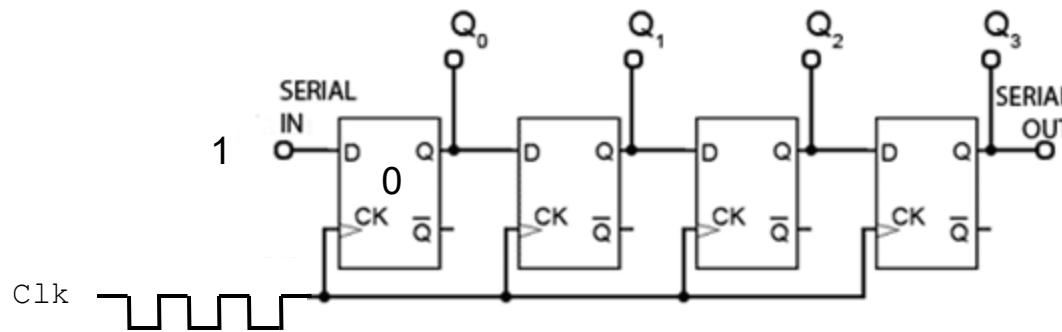

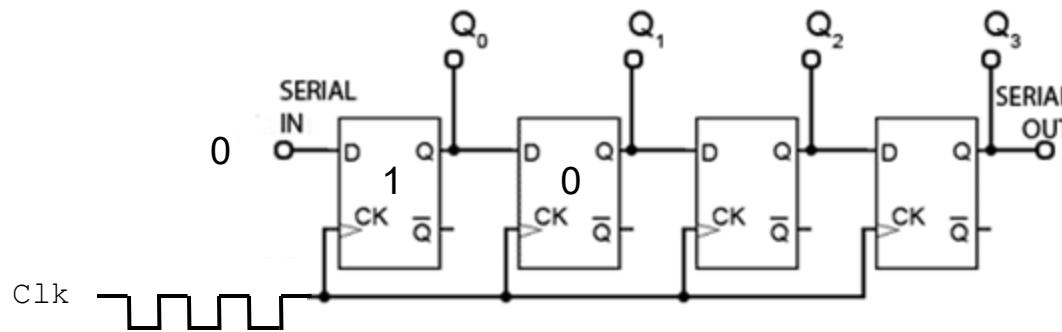

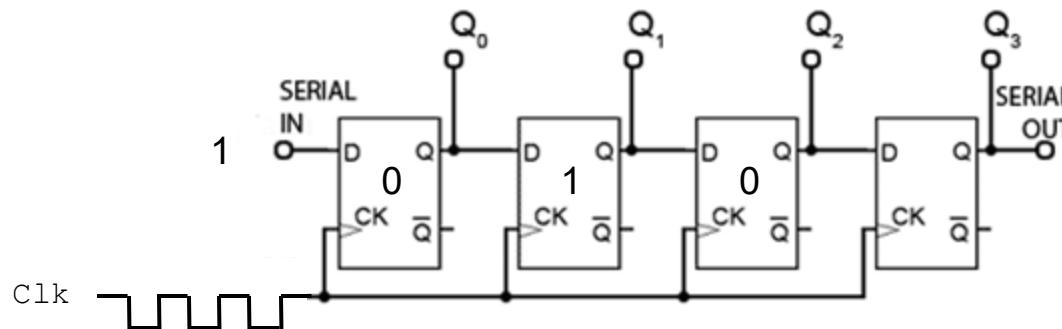

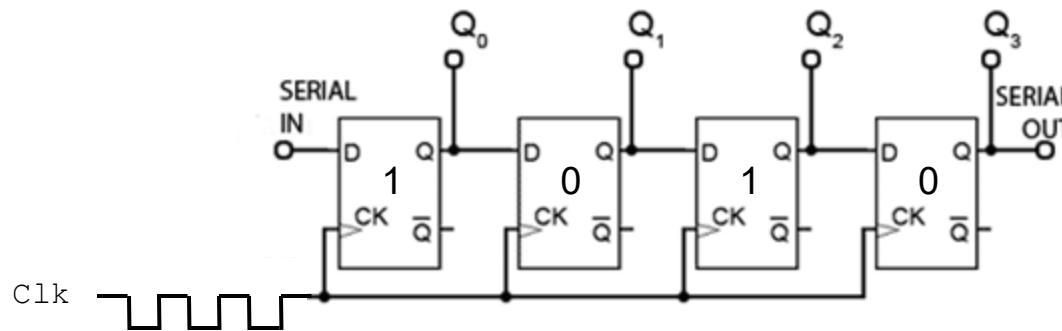

- This is a 4-bit register with serial loading:

# Registers

- This is a 4-bit register with serial loading:

# Registers

- This is a 4-bit register with serial loading:

# Registers

- This is a 4-bit register with serial loading:

# Registers

- This is a 4-bit register with serial loading:

# Registers

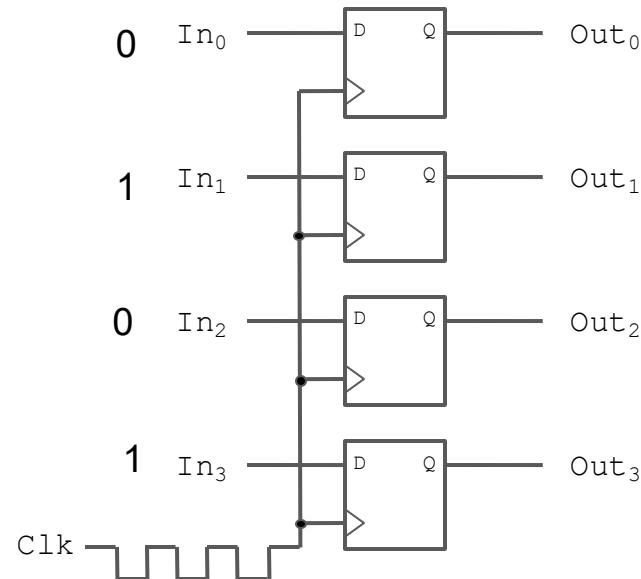

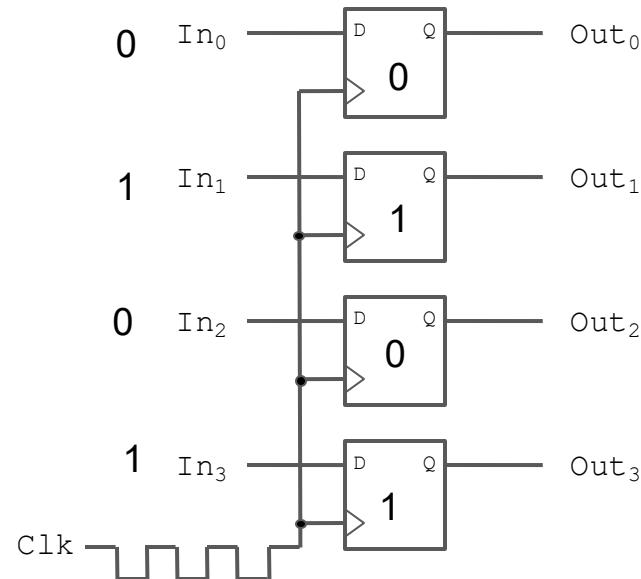

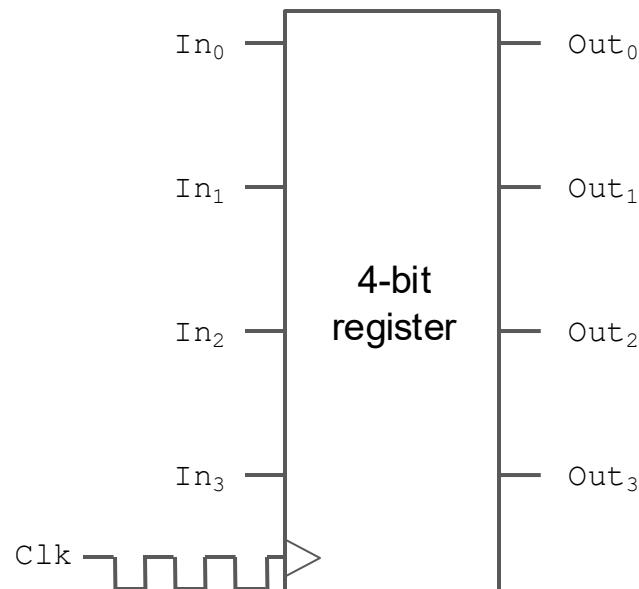

- This is a 4-bit register with parallel loading:

# Registers

- This is a 4-bit register with parallel loading:

# Registers

- This is the same 4-bit register shown in block notation:

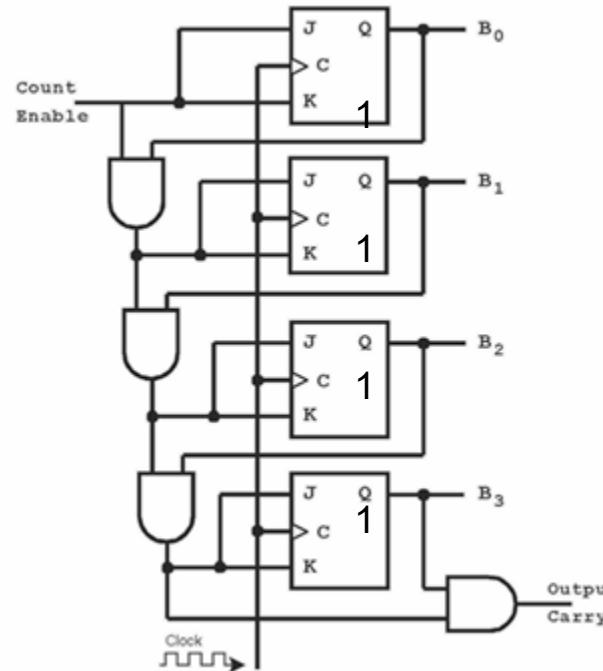

# Counters

- This is a 4-bit counter register:

- Useful for the program counter and general-purpose registers

# RAM

CSCI 2050U - Computer Architecture

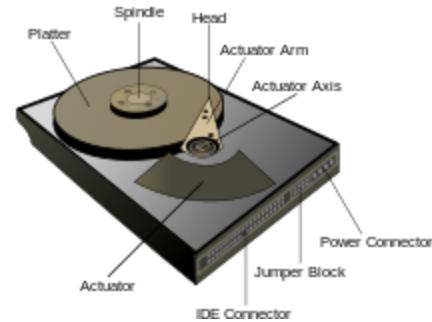

# Memory

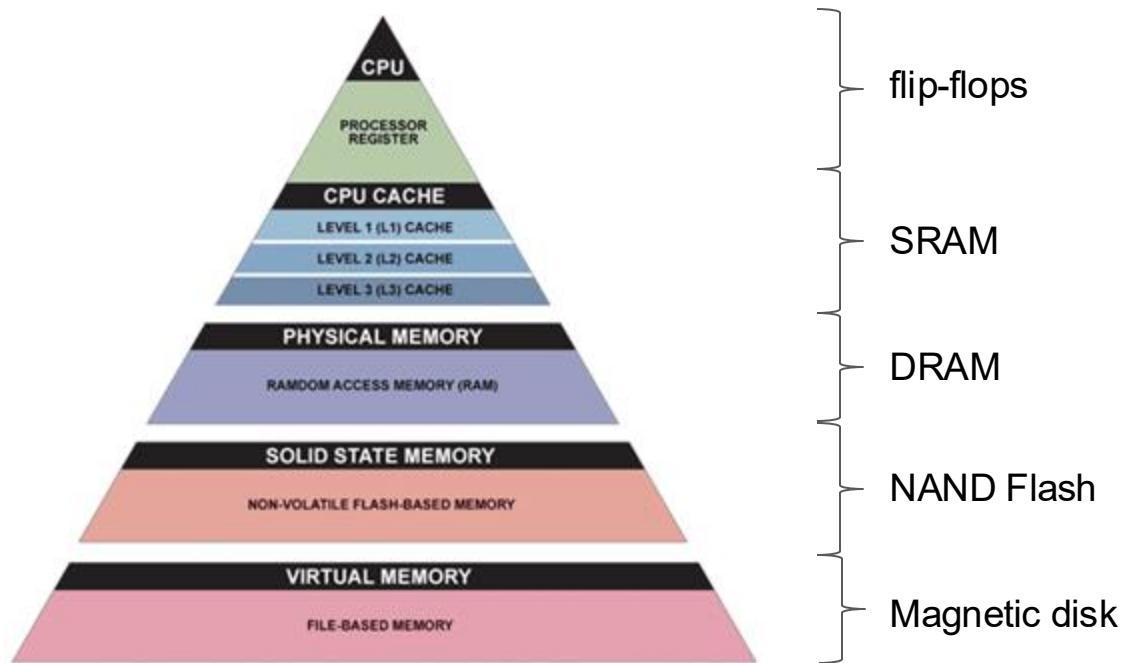

- Memory is implemented in several different ways:

- Magnetic - permanent, high-density, low-cost (HDD)

- Flash - permanent, high-density, low-cost (SSD)

- Capacitors - volatile, medium-density, medium-cost (DRAM)

- Flip flops - volatile, low-density, high-cost (SRAM, cache)

- Let's look at how we can implement this type of memory

- Other kinds of memory are discussed later:

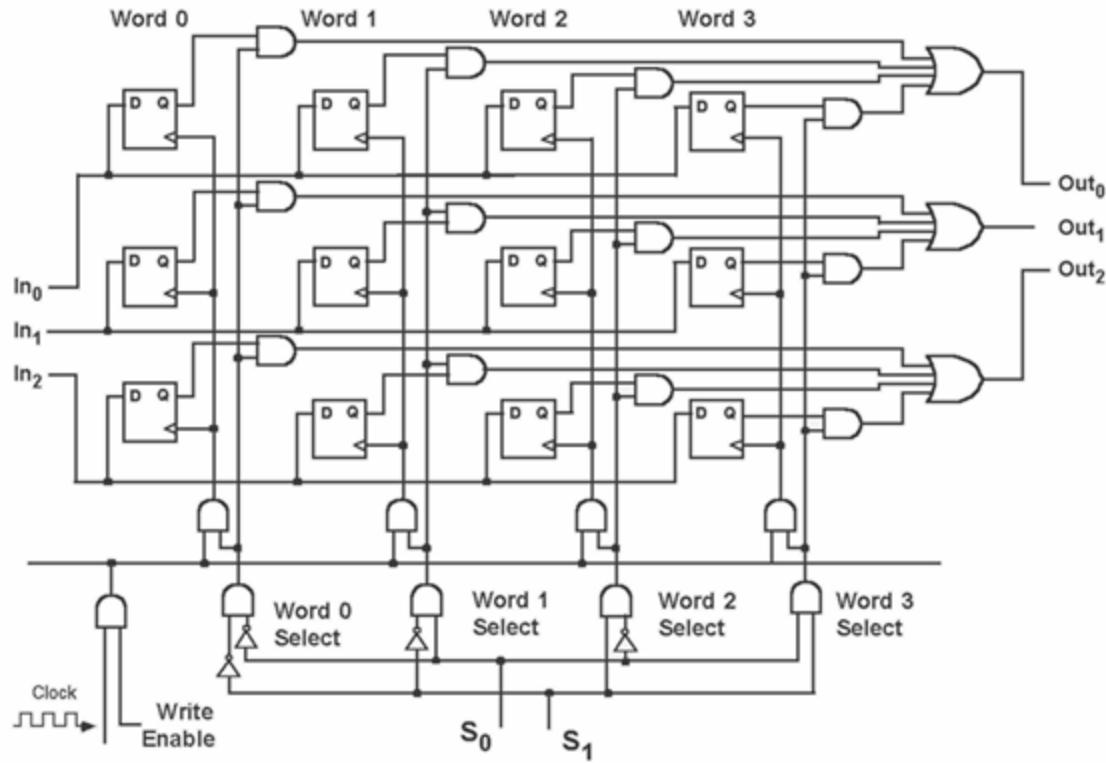

# Memory Arrays

- This is a 4x3-bit memory array

# The Memory Hierarchy

CSCI 2050U - Computer Architecture

# The Memory Hierarchy

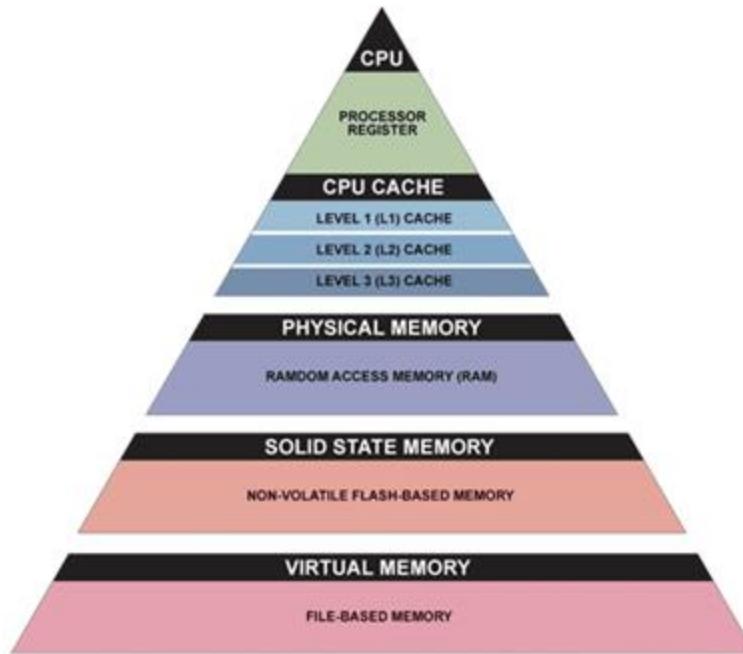

- All forms of memory can be organized into the following hierarchy:

# The Memory Hierarchy

- All forms of memory can be organized into the following hierarchy:

# Wrap-up

- Flip flops

- Registers

- Counters

- RAM

- The memory hierarchy

# What is next?

- Caching

- Virtual memory